ADC ENERGY EFFICIENCY EVOLUTION: What are the trends for ADC energy efficiency and why did the “Walden” figure-of-merit get almost canonical status when it doesn’t fit to current data? Read on, and you’ll know.

Evolution front

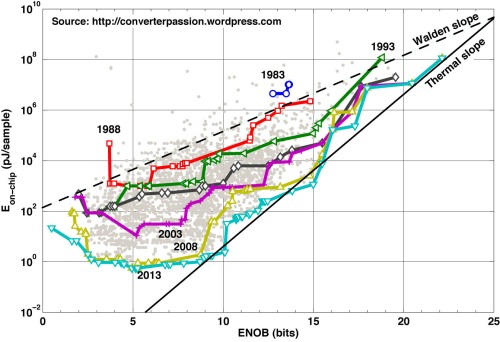

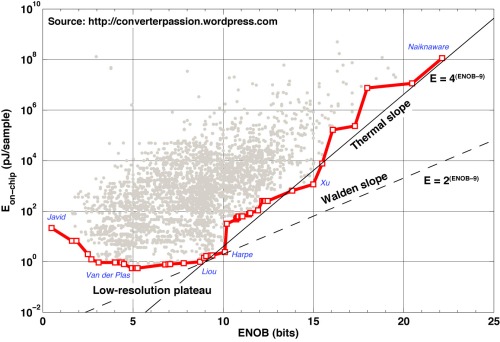

Figure 1 shows how the state-of-the-art boundary for energy-per-sample (Es) vs. effective-number-of-bits (ENOB) has progressed over time in 5-year steps from 1983 to 2013. The energy vs. resolution dependencies suggested by the Walden and Thermal figures-of-merit (FOM) have been indicated as the Walden and Thermal slope, respectively.

Snow cone scatter

The most immediately striking feature in Fig. 1 is that the curves are increasingly more separated at lower resolutions, and tend to group more closely together as ENOB increases. With the Thermal and Walden slopes overlaid as in Fig. 1, you get a kind of “snow cone scatter plot”. It means that the energy efficiency has improved far more for low-resolution ADCs than for high-resolution converters during the 30 years of research covered by Fig. 1. A possible explanation for that is the fairly low number of attempts reported above 15-b ENOB. Another reason could be that the power dissipation at ultra-high resolution almost inevitably becomes limited by thermal noise constraints, and that the few reported designs were carefully optimized. As an example, the work by Naiknaware et al. [1] is the only scientific ADC reporting an ENOB > 20-b (other works only report static linearity or measures that did not resolve to an SNDR value). Although Naiknaware’s design was reported as early as year 2000, it is still on par with today’s noise-limited state-of-the-art. That’s quite impressive!

Slope twist

A second distinct feature in Fig. 1 is that the slope for Es vs. ENOB has changed over time from an almost perfect Walden FOM model (doubling of Es per additional bit) to an almost perfect Thermal FOM model (quadrupling of Es per additional bit).

This explains the great mystery of the Walden FOM and its near-canonical status: Even as late as 2003, the state-of-the-art edge aligned very well with a Walden model. In fact, the Walden model remained true to empirical data all the way to 2007. By 2008, however, the experimental data had started to break away from the Walden slope – something that was also noted by Murmann in his well-known CICC 2008 paper [2] – and by 2013 the experimental data fits more or less perfectly with the thermal-noise model.

The van Elzakker leap

The single most influential contribution to this shift is probably that by van Elzakker et al. [3] as it represented nothing less than a quantum leap in energy efficiency for ADCs in the lower mid-range of resolutions. It gave us a new experimental data-point that completely redefined the energy landscape as it showed their medium-resolution design to be pushed all the way to the thermal-noise power limit of 2008. I believe their contribution broke a mental barrier for many regarding how far you can actually go, and what is the real energy limit. Over the last five years, other authors have followed by reporting more experimental data – both filling the gap created by the van Elzakker leap and pushing efficiency even further [4]-[6].

Low-resolution plateau

As always, we have the low-resolution plateau. There is a slight tendency towards a plateau already in the 1998 curve, and by 2003 it was fully visible – although at a much higher Es level than today’s plateau. Figure 1 also shows us that there has been significant progress at resolutions below 9-b over the 20 years from 1988 to 2008, but almost no movement at all during the last 5 years. The relative amount of attempts below 9-b (~35%) has remained the same both before and after 2008, so it should not be due to lack of interest.

Any explanations you might have would be very interesting to hear. Pure speculations are fine too 😉

Hopes and expectations for the future

In coming years I would expect to see progress in the 10–13 bit region, which seems to be a bit underexplored at the moment. We saw an extension in this direction by the most recent state-of-the-art work by Harpe et al. [4]. I hope that future authors will continue to push the resolution for ultra-efficient ADCs. It should be possible to “iron out the wrinkles” on the current state-of-the-art border. It would be particularly nice if we could populate the border with evenly spaced SAR implementations spanning all the way up to the high resolution of commercial SAR ADCs.

I also hope that someone will explore the empty space below the low-resolution plateau. It seems to be a lot of data points missing there that could give us a better understanding of the true energy limits.

More data at ultrahigh resolution – please!

Finally, I want to plead to those of you designing ultrahigh resolution ADCs to start including traditional dynamic performance measures (at least SNDR) even if the target application you’re imagining doesn’t care about it. If nothing else, it would increase your visibility in my scatter plots, but the main benefit for our science is that we would get more experimental data and a better understanding of the design space for “20-b and beyond”.

So, please … 🙂

References

- R. Naiknaware, and T. Fiez, “142dB ∆∑ ADC with a 100nV LSB in a 3V CMOS Process,” Proc. of IEEE Custom Integrated Circ. Conf. (CICC), Orlando, USA, pp. 5-8, May, 2000.

- B. Murmann, “A/D converter trends: Power dissipation, scaling and digitally assisted architectures,” Proc. of IEEE Custom Integrated Circ. Conf. (CICC), San Jose, California, USA, pp. 105–112, Sept., 2008.

- M. van Elzakker, E. van Tuijl, P. Geraedts, D. Schinkel, E. Klumperink, and B. Nauta, “A 1.9μW 4.4fJ/Conversion-step 10b 1MS/s charge-redistribution ADC,” Proc. of IEEE Solid-State Circ. Conf. (ISSCC), San Francisco, California, pp. 244–245, Feb., 2008.

- C.-Y. Liou, and C.-C. Hsieh, “A 2.4-to-5.2fJ/conversion-step 10b 0.5-to-4MS/s SAR ADC with Charge-Average Switching DAC in 90nm CMOS,” Proc. of IEEE Solid-State Circ. Conf. (ISSCC), San Francisco, USA, pp. 280–281, Feb., 2013.

- P. Harpe, E. Cantatore, and A. van Roermund, “A 2.2/2.7fJ/conversion-step 10/12b 40kS/s SAR ADC with Data-Driven Noise Reduction,” Proc. of IEEE Solid-State Circ. Conf. (ISSCC), San Francisco, USA, pp. 270–271, Feb., 2013.

- H.-Y. Tai, H.-W. Chen, and H.-S. Chen, “A 3.2fJ/c.-s. 0.35V 10b 100KS/s SAR ADC in 90nm CMOS,” Symp. VLSI Circ. Digest of Technical Papers, Honolulu, USA, pp. 92–93, June, 2012.

![FOM-vs-Year-by-DSM-Nyquist [monotonic SotA]](https://converterpassion.files.wordpress.com/2012/08/fom-vs-year-by-dsm-nyquist-monotonic-sota.jpg?w=500&h=341)