![Thermal-FOM-vs-Year-by-DSM-Nyquist [monotonic SotA]](https://converterpassion.files.wordpress.com/2012/08/thermal-fom-vs-year-by-dsm-nyquist-monotonic-sota.jpg?w=500&h=341)

Figure 1. Evolution of best reported thermal FOM for delta-sigma modulators (o) and Nyquist ADCs (#). Monotonic state-of-the-art improvement trajectories have been highlighted. Trend fit to state-of-the-art points for DSM [1984–2000] (dotted), and Nyquist [1982–2012] (dashed). Average trend for all designs (dash-dotted) included for comparison.

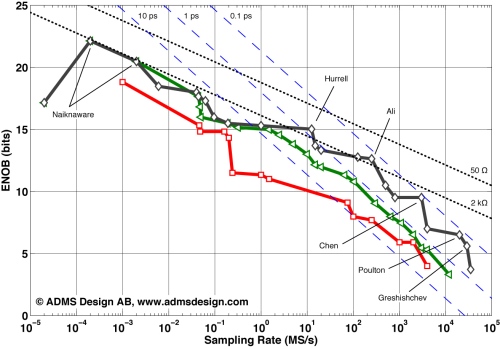

The thermal FOM considers error power rather than amplitude (as in the Walden FOM), and therefore the value of FB1 improves by 4× (rather than 2×) for every additional bit of resolution. This matches the theoretical 4× minimum increase in power if ENOB is limited by kT/C-noise [3] and the architecture remains unchanged [4]. It was shown in [5] that the thermal FOM represents a better description of the state-of-the-art power-resolution tradeoffs according to empirical data than the Walden FOM for ENOB ≥ 9.

As seen in Fig. 1, there is a significant difference between DSM and Nyquist ADCs with respect to FB1. With the exception of two early 14-b designs [6]-[7], the global state-of-the-art is defined entirely by delta-sigma modulator implementations while Nyquist ADCs lag distinctly behind. A possible explanation could be that the thermal FOM favors converters whose power dissipation is truly limited by thermal noise, and that high-resolution ∆-∑ ADCs are more distinctly driven into the thermal noise limit than their Nyquist counterparts. Another point is that many scientific DSM implementations use an off-chip (i.e., zero power) decimation filter implemented in software. This will give DSM an unfair advantage over Nyquist, although it can hardly be the only explanation for a one order of magnitude FOM difference.

Since the thermal FOM for Nyquist converters has evolved over a rather uneven path, I’ll not make any elaborate interpretations of its shape. The trend (dashed) is simply fitted to all the state-of-the-art points from 1982–2012, revealing an average improvement rate of 2× every two years. The DSM envelope appears to have three main segments with breakpoints at 1990 and 2000, respectively. For simplicity, a single trend was estimated for the envelope until Naiknaware [8], after which the thermal FOM has evolved significantly slower. From Fiedler [9] to Naiknaware, the average improvement rate is 2× every 17 months (1.4 years) – again faster than Moore’s Law [10]-[11] – whereas from year 2000 to present day [12], the state-of-the-art points fit to a more modest 2×/5.5 years slope. Even if the latter is from a fit of only four data points, and the exact slopes can be discussed, it is clear from Fig. 2 that the thermal FOM for DSM experienced a distinct slowdown after year 2000. This coincides with the breakpoint where the relative noise floor – approximately the denominator in (1) – also goes into saturation. It can further be noticed that it coincides with the accelerated evolution of FA1 as well. A possible, but perhaps speculative interpretation is that the ADC community first focused on thermal noise performance and related design optimization, and after hitting the noise floor around year 2000 moved on to focus on power efficiency.

If you wish to suggest other explanations, please share them below.

This concludes a series of ten posts on ADC performance and technology trends. If you want to go back and read them all from the beginning, these are the topics and the order in which they were posted:

- CMOS node adoption

- Low-voltage operation – part 1

- Low-voltage operation – part 2

- Thermal noise

- Jitter

- Relative noise floor

- Linearity (SFDR)

- Sampling rate and resolution

- Walden FOM

- Thermal FOM (this post)

As a small postlude, a follow-up post will list known prior art ADC surveys for those of you that (like myself) have an insatiable appetite for technology trend estimations and empirical data dots.

See also …

References

- A. M. A. Ali, C. Dillon, R. Sneed, A. S. Morgan, S. Bardsley, J. Kornblum, and L. Wu, “A 14-bit 125 MS/s IF/RF sampling pipelined ADC with 100 dB SFDR and 50 fs jitter,” IEEE J. Solid-State Circuits, Vol. 41, pp. 1846–1855, Aug, 2006.

- C. Wulff, and T. Ytterdal, “Design of a 7-bit, 200MS/s, 2mW pipelined ADC with switched open-loop amplifiers in a 65nm CMOS technology,” Proc. of NORCHIP, Aalborg, Denmark, Nov., 2007.

- B. Murmann, “A/D converter trends: Power dissipation, scaling and digitally assisted architectures,” Proc. of IEEE Custom Integrated Circ. Conf. (CICC), San Jose, California, USA, pp. 105–112, Sept., 2008.

- K. Bult, “Embedded analog-to-digital converters,” Proc. of Eur. Solid-State Circ. Conf. (ESSCIRC), Athens, Greece, pp. 52–60, Sept., 2009.

- B. E. Jonsson, “Using Figures-of-Merit to Evaluate Measured A/D-Converter Performance,” Proc. of 2011 IMEKO IWADC & IEEE ADC Forum, Orvieto, Italy, pp. 1–6, June 2011. [PDF @ IMEKO]

- R. J. van de Plassche, and H. J. Schouwenaars, “A Monolithic 14 Bit A/D Converter,” IEEE J. Solid-State Circuits, Vol. SC-17, pp. 1112-1117, Dec., 1982.

- T. Sugawara, M. Ishibe, H. Yamada, S.-I. Majima, T. Tanji, and S. Komatsu, “A Monolithic 14 Bit/20 µs Dual Channel A/D Converter,” IEEE J. Solid-State Circuits, Vol. SC-18, pp. 723-729, Dec., 1983.

- R. Naiknaware, and T. Fiez, “142dB ∆∑ ADC with a 100nV LSB in a 3V CMOS Process,” Proc. of IEEE Custom Integrated Circ. Conf. (CICC), Orlando, USA, pp. 5–8, May, 2000.

- H. L. Fiedler, and B. Hoefflinger, “A CMOS Pulse Density Modulator for High-Resolution A/D Converters,” IEEE J. Solid-State Circuits, Vol. SC-19, pp. 995-996, Dec., 1984.

- G.E. Moore, “Cramming more components onto integrated circuits,” Electronics, Vol. 38, No. 8, Apr. 1965.

- G. E. Moore, “No exponential is forever: but “forever” can be delayed!,” IEEE ISSCC, Dig. Tech. Papers, San Francisco, CA, Feb. 2003, pp. 20–23.

- J. Xu, X. Wu, M. Zhao, R. Fan, H. Wang, X. Ma, and B. Liu, “Ultra Low-FOM High-Precision ΔΣ Modulators with Fully-Clocked SO and Zero Static Power Quantizers,” Proc. of IEEE Custom Integrated Circ. Conf. (CICC), San Jose, California, USA, pp. 1–4, Sept., 2011.

![FOM-vs-Year-by-DSM-Nyquist [monotonic SotA]](https://converterpassion.files.wordpress.com/2012/08/fom-vs-year-by-dsm-nyquist-monotonic-sota.jpg?w=500&h=341)